Cadence DDR5 Update: Launching at 4800 MT/s, Over 12 DDR5 SoCs in Development

by Anton Shilov on March 27, 2020 2:00 PM EST

JEDEC still has not published the DDR5 specification officially, yet it looks like DRAM makers and SoC designers are preparing for the DDR5 launch at full steam. Cadence, which was vocal about the new technology back in 2018, and has since released provisional DDR5 IP (the DDR5 controller and PHY) commercially, this week presented some additional information about the upcoming DDR5 market release as well as the technology's progress.

DDR5 Platforms Getting Ready

On the SoC side of matters, we already know that AMD’s EPYC ‘Genoa’ as well as Intel’s Xeon Scalable ‘Sapphire Rapids’ will support DDR5 DRAM when they launch in the 2021 ~ 2022 timeframe. What is noteworthy, is that Cadence’s provisional DDR5 IP has ‘over a dozen design-ins’, so there are over 12 SoCs supporting DDR5 in various stages of development right now. Some of these system-on-chips will come earlier and some will be available later, but it is evident that there is a serious interest towards the technology among developers of SoCs.

Cadence is confident that its DDR5 controller and PHY are compliant to the formal JEDEC specification, so SoCs that use its IP will be compatible with upcoming DDR5 memory modules.

Cadence's DDR5 testboard with a module on it

Cadence's DDR5 testboard with a module on it

Here is what Marc Greenberg, director of DRAM IP marketing at Cadence, said:

“Close participation in the JEDEC working groups is an advantage. We get insight into how the standard will develop. We are a controller and PHY vendor and can anticipate any potential changes on the way to final standardization. In the early days of the standardization, we were able to adopt standard elements under development and work together with our partners to get very early working silicon. As we approach the release of the standard, we get more proof points to indicate that our IP will support DDR5 devices compliant to the standard.”

For Starters: 16 Gb DDR5-4800

Transition to DDR5 represents a major challenge for DRAM makers because the chips are set to increase capacity, rise data transfer rates, increase effective performance (per clock and per channel), and lower power consumption all at the same time (read more here and here). In addition, DDR5 is expected to make it easier to stack multiple DRAM devices, which will allow to increase DRAM capacity in servers (from what we have today).

Micron and SK Hynix have already announced sampling to partners of their DDR5 memory modules based on their 16 Gb chips. Samsung has not formally confirmed any sampling, but we know from its ISSCC 2019 announcement that the company has been preparing and evaluating its 16 Gb DDR5 devices and modules on internally for a while now. Anyhow, DDR5 will likely be available at launch from all three major DRAM producers.

Cadence is confident that DDR5 ramp will begin with 16 Gb DRAMs at 4800 MT/sec/pin data transfer rate (something that was indirectly confirmed by SK Hynix’s DDR5-4800 module showcase at CES 2020). From there, DDR5 will evolve in two directions: capacity and performance. Capacity wise, DDR5 will grow to 24 Gb (so expect DDR5 modules of odd capacity like 24 GB, 48 GB, etc.) and then to 32 Gb. As for performance, Cadence expects DDR5 to evolve to 5200 MT/sec/pin data rate in 12 – 18 months after DDR4-4800 launch and then to 5600 MT/s in another 12 – 18 months, so performance progress of DDR5 in servers will occur in a pretty much regular cadence.

On the client side, a lot will depend on controllers and memory module vendors, but enthusiast-grade DIMMs will certainly be faster than those used in servers.

Mr. Greenberg, said the following:

“DDR4 went to 3200 just this year. Adoption of DDR speed grades happens quite slowly. DDR5 is the next step. It is a big leap in bit rate performance. But it will then hang there for 12-18 months, then go up to 5200, and 5600 after that. We are back on the treadmill of one speed grade every 12-18 months.”

In fact, the step from DDR4-3200 to DDR5-4800 will bring a huge performance bump, but it does not end there for servers. Because of 16 Gb chips, internal DDR5 architecture optimizations, new server architectures, and usage of RDIMMs instead of LRDIMMs, single-socket systems with 256 GB DDR5 modules will get a nice performance increase in terms of latency (vs. today’s LRDIMMs).

Here is what Mr. Greenberg said:

“A lot of these machines have 8 channels on a processor [socket], each [channel] with 512 GB, making a 4 TB memory machine where you can access any byte in under 100 ns. If a database index is 4 TB, you can imagine how big a database could be supported. Quite a beast.”

Keeping in mind that AMD’s EPYC ‘Rome’ CPUs already have eight memory channels and support up to 4 TB of DDR4 DRAM per socket using 256 GB RDIMMs, one can take advantage of low latency (vs. LRDIMMs) even today, but not at DDR5’s speeds. Meanwhile, systems with LRDIMM support can have up to 4.5 TB per socket, but at a cost of additional latency.

DDR5 Shipping This Year?

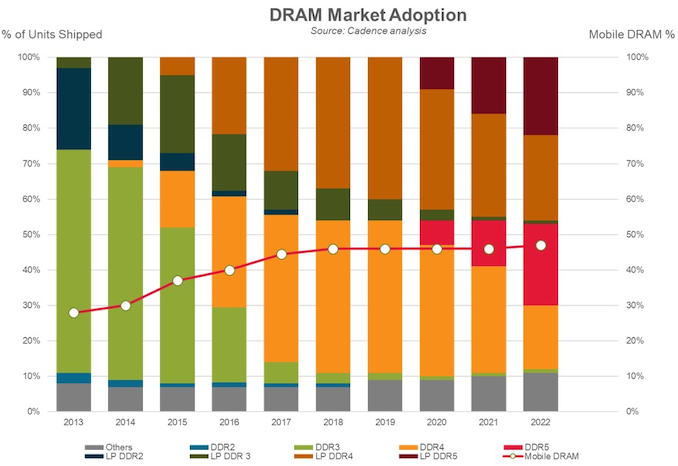

As noted above, AMD’s Genoa and Intel’s Sapphire Rapids are not due until very late 2021, or rather early 2022, but Cadence seems to be optimistic and believes that ‘2020 will be the year of DDR5’. From Cadence’s perspective, this might mean tapeouts of actual DDR5-supporting SoCs (which is about time), but the company’s internal analysis shows that it expects DRAM vendors to actually start shipments of DDR5 memory this year.

Memory makers tend to start volume shipments of new types of DRAM ahead of general availability of platforms. Meanwhile, shipping a year before AMD’s Genoa and Intel’s Sapphire Rapids seems a bit early, but has several reasonable explanations: AMD’s and Intel’s DDR5-supporting processors are closer than communicated by the two companies, there are DDR5-supporting SoCs that are coming to market well ahead of those from AMD and Intel, system makers need time to test DDR5 modules and stock them ahead of major product launches.

In any case, if the DDR5 specification is at the Final Draft stage, it is possible for major DRAM makers to kick off volume production even without a published standard. Theoretically, SoC developers can also send their designs to manufacturing at this stage. Meanwhile, it is hard to imagine DDR5 to capture any sizeable market share in 2020 – 2021 timeframe without support from the major CPU vendors.

Related Reading:

- Cadence and Micron Demo DDR5-4400 IMC and Memory, Due in 2019

- Cadence & Micron DDR5 Update: 16 Gb Chips on Track for 2019

- Keysight Reveals DDR5 Testing & Validation System

- Here's Some DDR5-4800: Hands-On First Look at Next Gen DRAM

- SK Hynix Details DDR5-6400

- SK Hynix Develops First 16 Gb DDR5-5200 Memory Chip, Demos DDR5 RDIMM

Source: Cadence

19 Comments

View All Comments

Khenglish - Friday, March 27, 2020 - link

I was hoping to see memory sticks jump from 64 bit to 128 bit, or at least 96 bit. A typical memory chip supports 32 bits of data width. With just 8 chips on a stick for 1 memory rank that's 256 bits of potential throughput, so that's not a bottleneck. Doing 128 bit would be easy. It's just a matter of board wiring density and cost.brucethemoose - Friday, March 27, 2020 - link

That would mean more pins on the socket as well, and perhaps unecessary cost on the low end with embedded stuff, IoT, mobile etc.Maybe future DDR revisions could diverge? LPDDRX keeps the narrow bus, while high end DDR uses more pins or maybe a different form factor (sockets?). Something will need to be done at the top end, as servers cant just keep bumping up per socket channel counts.

extide - Friday, March 27, 2020 - link

The type of memory chips used on memory sticks used in PC's (SDRAM, DDR1/2/3/4/5) are all 8-bits. GDDR5/X/6 uses 32-bit chips. That's why we have 64-bit sticks that have multiples of 8 chips on them (for non ECC). So yeah the sticks would be a lot more complex and expensive -- which is why we just use multiple sticks for wider interfaces. 2ch = 128-bit, 4ch = 256-bit, etc.dotjaz - Saturday, March 28, 2020 - link

Not all 8bit, there're also 4bit and 16bit widely in use.saratoga4 - Saturday, March 28, 2020 - link

>I was hoping to see memory sticks jump from 64 bit to 128 bitThat would defeat the purpose of DDR5. If you want more channel width at lower capacity, you're supposed to use GDDR or LPDDR.

psyclist80 - Friday, March 27, 2020 - link

Zen 3 is still AM4 and DDR4 isnt it? and thats not landing till this fall. So we wont see Zen 4, AM5 and DDR5 platform till fall 2021 then. Maybe Intel has made the jump to DDR5 for Rocket Lake and its LGA1700 socket. 2021 looks to be a good battle, and good time to build a new rig!Cygni - Friday, March 27, 2020 - link

This is all rumor, but the rumors are that Zen 3 will be a bit delayed, and Rocket Lake (a 14nm Tiger Lake) will use the same socket as Comet Lake. So it will still be DDR4 as well.Alder Lake would theoretically be the first DDR5 desktop part from Intel, and Zen 4 the first part from AMD, likely late in 2021 from both.

Again just rumor, so take it for what its worth.

Xajel - Sunday, March 29, 2020 - link

Which rumour said Zen 3 will be delayed?AMD officially have a 12~18 months cycle, Zen2 was launched in July-2019, so Zen3 can be launched anywhere from July-2020 to January-2021 without the excuse of being delayed.

The last I heard, they plan to launch it 4Q20, maybe October/November timeframe. So no delays of any sort here.

david@van.dromme.net - Monday, March 30, 2020 - link

I had a partner tell me that the new serverchips (EPYC 3) are goign to launch this summer, with availability later in the year.Santoval - Friday, March 27, 2020 - link

Zen 4 will have DDR5 controllers only if the final draft of DDR5 is published (or is given to them by JEDEC pre-publication) before the development of Zen 4 is completed. Otherwise DDR5 will need to wait for Zen 5 (in that case the AM5 socket will be DDR5 ready -even if Zen 4 does not have DDR5 controllers- and would need to have pins for both DDR4 & DDR5, which might be a bit troublesome).My educated guess is that AMD would never add DDR5 support to Zen 4 without having the final draft, because you never know what might change in the final spec at the last minute. It might be better to delay the release of Zen 4 a few months, if required, so that DDR5 support is added. AMD need DDR5 even more than Intel due to their higher number of cores. They need it because they cannot add more memory channels to Epyc (in particular) if they want to offer more than 64 cores. Zen 3 based Epyc CPUs will retain the 64-core limit, thus the next time to increase cores should be when they release Zen 4 based Epyc CPUs.

Zen 4 based APUs, in turn, should add support for LPDDR5. AMD could add such support to their Zen 3 based APUs as well, due to the quite earlier availability of LPDDR5, but I doubt they will.